共同利用(産業利用トライアルユース: 先端研究施設共用促進事業 『みんなのスパコン』TSUBAMEによるペタスケールへの飛翔) 成果報告書 平成24年度 商用アプリバンドル型トライアルユース

利用課題名 静電気シミュレーションにおけるモデルの簡略化に関する一考察 英文: A consideration for the simplification of the models in the ESD simulation.

# 利用課題責任者 芹澤孝宜

Takayoshi Serizawa

# 所属 東芝テック株式会社 Affiliation TOSHIBA TEC CORPORATION URL http://www.toshibatec.co.jp

## 邦文抄録(300字程度)

近年、主要な IC の電源電圧が低下する傾向があり、微量なノイズの混入が IC の誤動作を引き起こすようになってきた。イミュニティの試験として、製品開発では静電気(ESD: Electro-Static Discharge)試験を実施しているが、誤動作が発生した場合の原因究明や対策には、今まで以上に時間を必要としている。ESD 解析では、IC の電源 GND 間端子に発生する電圧リプルを計算するために、解析対象はプリント基板を含む大規模なモデルとなる。このような大規模なモデルを解析するための環境として、TSUBAME2.0 を使用して解析した結果、適切な簡略化によって良好な解析結果が得られることが分かった。設計段階で EMC(Electro Magnetic Compatibility)の検証を行うことを目的に CST STUDIO SUITE を導入し、活用を進めている。

## 英文抄録(100 words 程度)

Recently, the invasion of a slight noise to printed circuit boards came to cause a trouble because the power supply voltage of the integrated circuit tended to lower. We carry out ESD (Electro-Static Discharge) examinations as the immunity test. We need time for investigation into causes, when a trouble occurred by the test. In the ESD simulation, it is necessary to calculate the ripple voltage between the power supply and the ground. Therefore the simulation models have to include printed circuit boards and become large. As a computer to simulate such the large-scale models, we used TSUBAME2.0. We understood that appropriate simplification provide enough results for development of products. We introduced CST STUDIO SUITE for EMC (Electro Magnetic Compatibility) design.

Keywords: Electro-magnetic field simulation, EMC, EMS, ESD, Immunity

#### 背景と目的

帯電した導電性の物体(例えば人体)が他の導電性の物体(例えば電子機器)に接触すると、放電が発生する。この現象は ESD と呼ばれ、電子機器の誤動作や損傷などの問題を引き起こし、場合によっては爆発、発火の引金となることもある。そのため、電子機器はそれに対する充分な耐性(ESD 耐性)を持つことが必要となる。この耐性を確認するための試験として静電気試験(IEC61000-4-2)が規定されている。

静電気試験は、試作段階で実施されている(図 1)。 試験では、ESD を製品に印可し、製品が誤動作しない ことを確認する。試験で誤動作が発生した場合には、 対策するための設計変更や部品追加が行われ、製品 のコストアップにつながってしまうことが多い。このよう な事態を避けるために、製品の構想または詳細設計段階で、静電気試験をシミュレーションすること(ESD 解析)が必要となっている。

図1 製品開発ステップ

静電気試験での誤動作は、製品の筐体に印加された ESD が、プリント基板に搭載された主要な IC(CPU, メモリなど)に対して、何らかの影響を及ぼしていると考 えられる。そのため、ESD 解析に用いるモデルは、プリ ント基板やハーネス、筐体などで構成される大規模な

#### (様式第20)成果報告書

モデルとなる。通常、大規模なモデルを扱う場合には、 計算を実行するハードウェアに合わせて、計算可能な 規模にモデルを簡略化していく必要がある。しかしなが ら、簡略化しすぎてしまうと問題となる現象を正確にシミ ュレータ上で再現できなくなってしまうこともある。

本課題では、大規模な ESD 解析モデルを TSUBAME2.0 を使用して計算する。解析の結果、 ESD 印加によってハーネスが共振し、CPU 電源を揺ら す現象を確認した。また、そのために必要な解析規模 を把握できた。

#### 概要

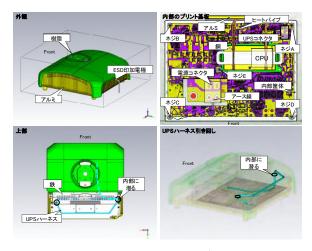

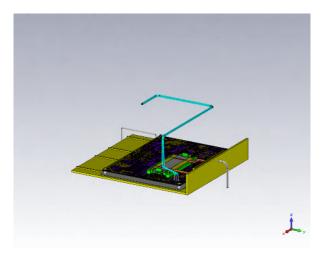

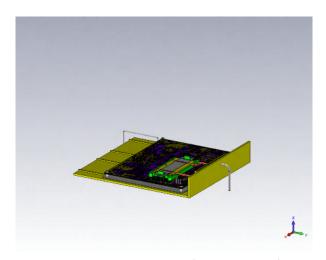

ESD 解析のターゲットとしたモデルを図 2 に示す。筐体、ハーネス、プリント基板を含む大規模なモデルとなった(4.7 億メッシュ)。 この製品は、静電気試験により、UPS(Uninterruptible Power Supply:無停電電源)に接続されるハーネスの有無が製品としての ESD 耐性に大きな影響を与えていることが確認された(表 1)。この現象を再現するためのモデルを図 3,4 に示す。ESD 耐性悪化の原因は、筐体からハーネスへの静電誘導か、または、ハーネスの共振であると考えられる。図 5 は、この二つの原因を切り分けるために、ハーネスを外に引出し、筐体からの静電誘導を受けないようにしたモデルである。図 6,7 は、簡略化したモデル(2.6 億メッシュ)である。

図 2 ESD 解析モデル

ESD 耐性が悪化した場合には、現象として画面ロックが起こる。これは、ESD 印加により、主要な IC の電

源 GND 端子間に電圧リプルが発生したためと考えられる。そのため、ESD解析では、ICの電源 GND 端子間に発生する電圧を観測する。

製品開発では、電気的な傾向を解析できれば良い場合がほとんどである。そのため、ESD 印加電極への入力として、ガンモデルは考慮せず、ガウシアンパルスの印加とした。解析モデルにプリント基板が含まれる場合、ガウシアンパルスの収束には多くの計算時間がかかるため、計算は 15ns で打ち切っている。

表 1 静電気試験結果

| 製品の状態     | 試験結果 | 不具合現象 |

|-----------|------|-------|

| UPSハーネス有り | NG   | 画面ロック |

| UPSハーネス無し | OK   | -     |

図3 UPS ハーネス有りモデル

図 4 UPS ハーネス無しモデル

## (様式第20)成果報告書

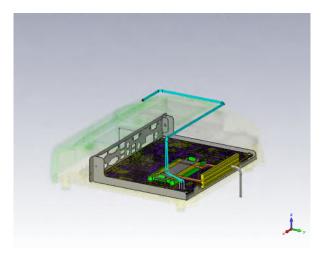

図 5 UPS ハーネス外出しモデル

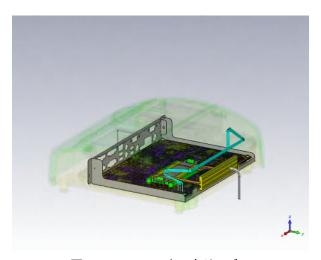

図 6 UPS ハーネス有りモデル(簡略化モデル)

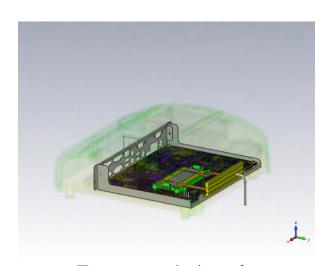

図 7 UPS ハーネス無しモデル(簡略化モデル)

## 結果および考察

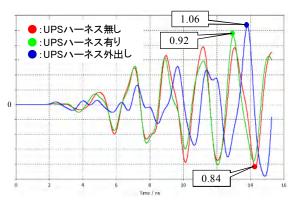

大規模モデル(図 3,4,5)の解析結果を図 8 に示す。 ESD の影響が CPU 電源の電圧リプルとして現れている。このリプルの絶対値は、「UPS ハーネス外出し> UPS ハーネス有り>UPS ハーネス無し」となっていることが分かる。静電気試験でOKであったハーネス無しの場合と比べて、ハーネス有りの場合、ハーネス外出しの場合は、ともに CPU 電源に大きな電圧リプルが発生しており、試験結果の傾向と、解析結果(CPU 電源に発生する電圧リプルの絶対値)の傾向が一致している。また、ハーネス外出しの場合に、最も大きな電圧リプルが発生していることから、ESD 耐性悪化の原因は、ハーネスの共振であることが判明した。

図8 CPU電源の電圧リプル

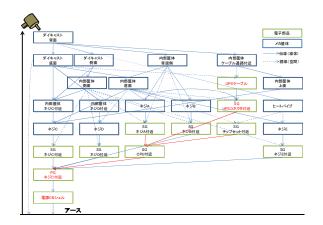

大規模なモデルの解析は、通常、実施が困難であるため、簡略化を行い解析規模を抑える必要がある。問題となった原因は、ハーネスの共振であったため、この現象と関係が薄い部分は簡略化が可能と考えられる。 ESD が流れると予想される経路(図 9)から、製品の上面や側面は共振との関係が薄いと予想される。この部分を簡略化したモデル(2.6 億メッシュ)を作成した(図 6,7)。

図9 ESD 経路の考察

#### (様式第20)成果報告書

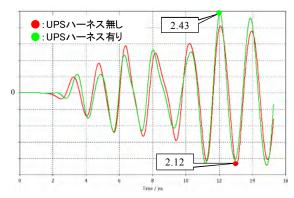

簡略化したモデルの解析結果を図 10 に示す。この電 圧リプルの絶対値は、「UPS ハーネス有り>UPS ハー ネス無し」となっており、試験の傾向と同じ傾向が現れ、 適切な簡略化ができたことが分かった。

図 10 CPU 電源の電圧リプル(簡略化モデル)

## まとめ、今後の課題

本課題では、ESD 解析を TSUBAME 2.0 を使用して計算し、静電気試験で起こる誤動作の原因がハーネスの共振であることを特定し、共振との関係が薄い部分を簡略化することで、解析規模を抑えることができた。解析モデルへの入力として、ガウシアンパルスを使用したが、静電気試験と同じ傾向が解析結果から得られた。

製品開発では、試験前に不具合を予測、または未然防止する必要がある。そのため、設計ルールの整備が今後の課題である。例えば、ESD電流は基本的にアースに戻るため、図 9 のような経路の中で、最もインピーダンスの低い経路を特定することで、そこから主要なICを離しておくなどの設計が可能となる。また、ESD印加ポイントが決まっていれば、そこからプリント基板に到達するまでの分岐を多くすることで、基板に流れ込む電流は減ると考えられる。ただし、今回のように、共振する可能性を常に考えることが重要である。

解析は、64MPI(GPU 不使用)とし、4.7 億メッシュモデルで 25H 程度、2.6 億メッシュモデルで 12H 程度かかった。