平成 26 年度 TSUBAME 産業利用トライアルユース 成果報告書

# 利用課題名 三次元電磁界シミュレータを用いた静電気放電イミュニティ試験に於ける PCB/Package/Chip のイミュニティ解析 (継続課題)

英文: Immunity analysis of PCB/Package/Chip in the electrostatic discharge test using the three-dimensional electromagnetic field simulator

## 賀 文寿、永野 民雄

Fumikazu Ga, Tamio Nagano

所属: ルネサスシステムデザイン株式会社

Affiliation: Renesas System Design Co., Ltd. URL: http://www.renesas.com/

静電気放電(ESD)イミュニティの実験環境を含む大規模モデルに対して、3次元電磁界シミュレータによる ESD イミュニティ解析を検討した。シミュレーションと実測の相関性を確認し、実用的な時間範囲内で解析できることを確認した。スーパーコンピューターTSUBAME による大規模 3次元電磁界解析は、ESD イミュニティ設計に有用であることを示した。

Electrostatic discharge (ESD) immunity analysis using 3-dimensional (3D) electromagnetic field simulator for large-scale models, including ESD immunity test environment, have been studied. The correlation between simulations and measurements is confirmed, and the analysis can be finished within a practical time. The large-scale 3D electromagnetic field analysis by the TSUBAME supercomputer is demonstrated to be useful in designing ESD immunity.

Keywords: 電磁界シミュレーション Electromagnetic field simulation、静電気放電 Electrostatic discharge (ESD)、イミュニティ Immunity、プリント回路基板 Printed Circuit Board (PCB)、大規模集積回路 Large Scale Integration (LSI)

## 背景と目的

電子機器の低電圧化、高速化に伴い、静電気が起因の誤動作が発生しやすくなってきている。静電気放電(ESD)による破壊や誤動作を防止するため、ESDイミュニティ試験[1]が規格化され、製品に対する ESDイミュニティ試験が行われている。

低コストで ESD イミュニティに強い PCB/Package/ Chip を設計するには、ESD イミュニティ試験でノイズ がどの経路をたどってチップに伝搬し、誤動作を引き起こしているかを理解することが重要である。一つのアプローチとして、3 次元電磁界シミュレーションによるノイズの可視化がある[2]、[3]。

一般の PC 環境では、基準グラウンド面、水平結合板、ESD ガン、PCB/Package/Chip 等を含む ESD イミュニティ試験の実環境を 3 次元電磁界シミュレータで解析することは、使用メモリ、解析時間の観点から困難である。

本プロジェクトでは、スーパーコンピューター

TSUBAME を利用し、ESD イミュニティ試験の 3 次元 電磁界解析を行い、ノイズの伝搬経路の可視化を含む ESD イミュニティの設計手法を構築することを目的とし た。

平成 25 年度に同課題名で、3 次元電磁界解析によるノイズ伝搬のメカニズムについて検討を行った。しかし、実機試験結果とシミュレーションとの比較考察には至らず、LSI モデルや、解析条件などについて課題が残る結果となった[4]。

本検討では、平成 25 年度の課題に対して、LSI モデル、ケーブルモデル、励起源などをより実体に合せて 3 次元電磁界解析を実施し、試験と解析結果は傾向一致という結果を得た。また、ノイズの伝搬経路の可視化を実施し、実用的な時間範囲内で解析できることを確認した。

前回と今回の検討を通じて、TSUBAMEによる大規模3次元電磁界解析は、ESDイミュニティ設計に有用であることを示した。

#### 概要

CST STUDIO SUITE 2014 を用いて[5]、ESD イミュニティ解析の検討を行った。

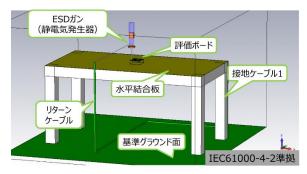

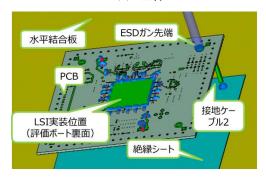

シミュレーションモデルを図 1 に示す。実試験環境に合わせて、基準グラウンド面、水平結合板、ケーブル、ESD ガン[6]、絶縁シート、PCB、LSI 等をモデル化した。図 1 のモデルを用いて 3D 電磁界解析を行い、試験との比較、ノイズの伝搬経路の可視化を行った。

(a) 全体

(b) 評価ボード周辺

図 1 シミュレーションモデル

#### 結果および考察

PCB 上電源配線パターンが共通と分離の 2 種類の評価ボード(以降、電源共通ボードまたは電源分離ボードと呼ぶ)に対して、IEC61000-4-2 に準拠した試験環境で、ESD ガンによる接触放電試験を実施した。

試験結果により、LSI の誤動作耐圧は、電源共通ボードより電源分離ボードの方が低い。よって、LSI に伝搬するノイズは、電源分離ボードの方が大きいと考えられる。

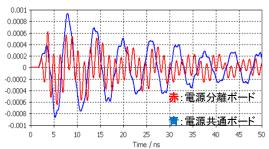

図 2 に Chip の電源端子でのノイズ波形のシミュレーション結果を示す。図 2(a)に前年度モデルのノイズ 波形を示すように、LSI に伝搬するノイズは電源共通 ボードの方(青線)が大きい。この結果は試験傾向と異なる。

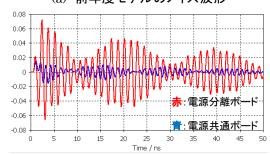

そこで、下記のモデル改良を行い、3 次元電磁界解析を実施した。

- -LSI モデルの電源構造を改良する

- ーケーブルモデルの長さ、設置状態をより実体に 合わせる

- -ESD ガンの出力は実測に合うように、励起信号を 調整する

図 2(b)に改良モデルのノイズ波形を示す。LSI に伝搬するノイズは電源分離ボードの方(赤線)が大きい。 試験と解析結果は傾向一致という結果が得られた。

ノイズの伝搬経路を可視化した表面電流分布を図3に示す。TSUBAMEを使用して、図1に示すモデル全体の表面電流分布が得られた。しかし、表示用PCマシンの性能制限で、局部の表面電流分布しか表示できず、課題があった。

(a) 前年度モデルのノイズ波形

(b) 改良後モデルのノイズ波形

図2 シミュレーション結果

図3 表面電流分布

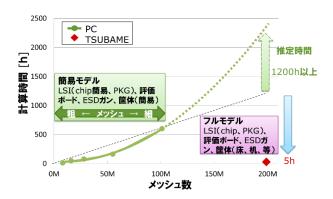

今回のシミュレーション時間を表 1 に示す。約 200M メッシュ規模のモデルに対して、TSUBAME の 4 ノードでの計算時間は約 5 h であり、実用的な時間範囲内で解析できることを確認した。

PCとTSUBAME の計算時間の比較を図 4 に示す。一般的な PC 環境で、基準グラウンド面、水平結合板、ESD ガン、PCB/Package/Chip 等を含む ESD イミュニティ試験の実環境を解析すると、推定の計算時間は 1200 h 以上となる。一方、TSUBAME での計算時間は約 5 h で、240 倍以上の時間短縮効果が得られた。

表 1. シミュレーション時間

| メッシュ数 | 使用ノード数* | 計算時間 |

|-------|---------|------|

| 200M  | 4       | 5 h  |

\*1 ノード: 12CPU コア、3GPU

図4 PCとTSUBAME の計算時間の比較

#### まとめ、今後の課題

TSUBAME を利用して、ESD イミュニティの実験環境を含む大規模モデルに対して、3次元電磁界解析を実施した。

LSI モデル、ケーブルモデル、励起源などをより実体に合せて3次元電磁界解析を実施した結果、試験と解析結果は傾向一致の結果を得た。また、200M メッシュ規模のモデルに対して、TSUBAME の4ノードでの計算時間は約5h であった。これらの結果から、TSUBAME による大規模モデルの ESD イミュニティ解析の実用性を確認できた。本技術はノイズの可視化、誤動作のメカニズム解明、イミュニティ設計・対策の応用に期待される。

ノイズの可視化の検討を行った。しかし、大規模モデルのノイズ可視化データに対して、表示用 PC マシンの性能が追いつかず、全体表示困難の課題があった。

今後、メッシュ数を削減して、計算の高速化、表示の 容易化を図る。

### 謝辞

本プロジェクトにおきまして、多くのご支援を頂いた東京工業大学学術国際情報センター共同利用推進室、 CST STUDIO SUITE ソフトウェアのサポートを頂いた 株式会社エーイーティーに深く感謝いたします。

#### 参考文献

- [1] IEC61000-4-2, Testing and measurement techniques Electrostatic discharge immunity test, Edition 2.0, 2008.12

- [2] http://www.fujitsu.com/jp/solutions/businesstechnology/tc/fields/cae/poynting/esd-pcbchassis.html

- [3] 賀 文寿, 秋山 雪治, 白井 淳一, "電磁界シミュレーションによる ESD イミュニティの解析"2013 年第 27 回エレクトロニクス実装学会春季講演大会 14C-11

- [4] 秋本 哲也, "三次元電磁界シミュレータを用いた 静電気放電イミュニティ試験に於ける PCB/Package/hip のイミュニティ解析"平成26 年度 東京工業大学 TSUBAME 産業利用シン ポジウム pp.147~150

- [5] https://www.cst.com/

- [6] S. Caniggia, F. Maradei, "Circuit and Numerical Modeling of Electrostatic Discharge Generators," IEEE Transactions on Industry Applications, Vol. 42, pp. 1350-1357, Nov. 2006.