# Dealing with Deeper Memory Hierarchy in Post-Petascale Era

## **Project Overview**

### **Target Architecture**

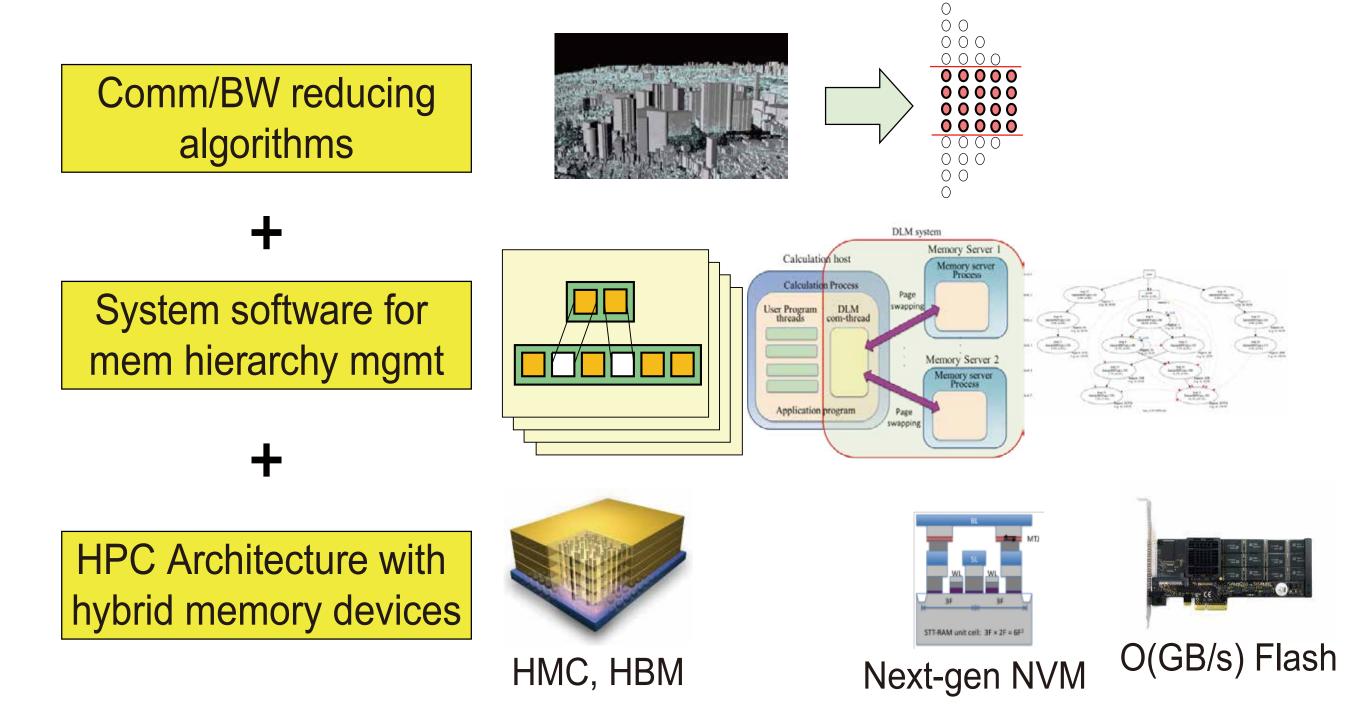

On Exa-scale supercomputers, the "Memory Wall" problem will become even more severe, which prevents the realization of Extremely Fast&Big Simulations.

This project promotes research towards this problem via co-design approach among application algorithms, system software, architecture.

We consider near future HPC systems where each node has deeper memory hierarchy that consists of heterogeneous memory including NVM. We do not exclude usage of shared layer such as burst buffers.

10

Target: Realizing Extremely Fast&Big simulations of O(100PB/s) & O(PB) in Exa-scale era

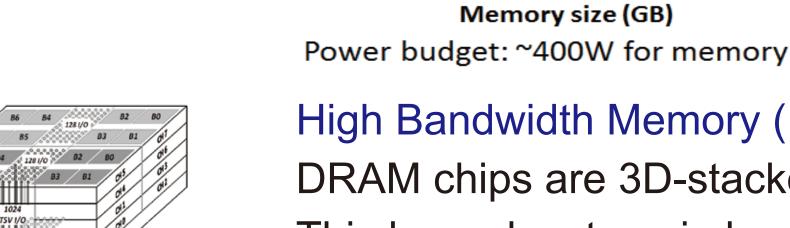

High Bandwidth Memory (HBM):

DRAM chips are 3D-stacked with TSV technology. This has advantage in bandwidth over traditional DDR, but capacity tends to be limited.

10000

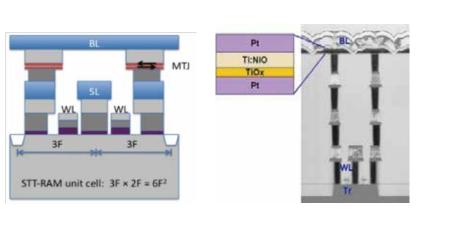

### Next-Gen Non-volatile Memory (NVM):

1000

Several kinds of NVM such as STT-MRAM, ReRAM, FeRAM, 3D Xpoint will be available in near future. They have different properties in BW and capacity.

### NAND Flash devices:

Not only SSDs with traditional SATA/SAS interfaces, but recent PCIe/m.2 SSDs with O(GB/s) bandwidth are already available.

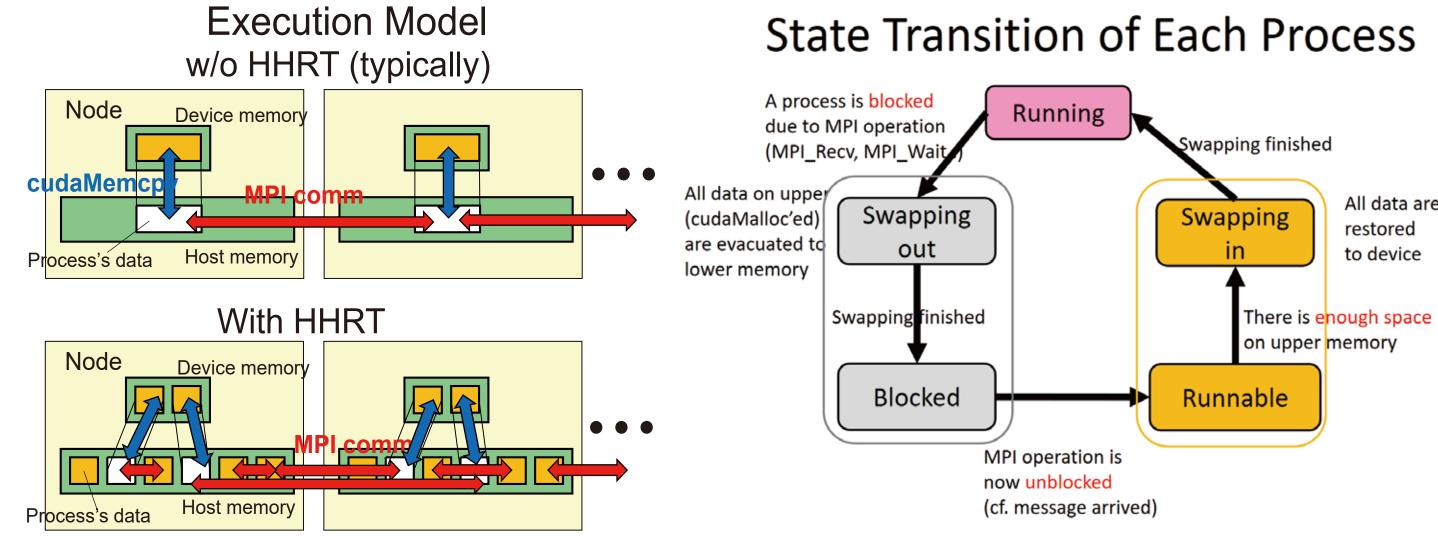

HHRT: System Software for Swap

# Integration with App Algorithm

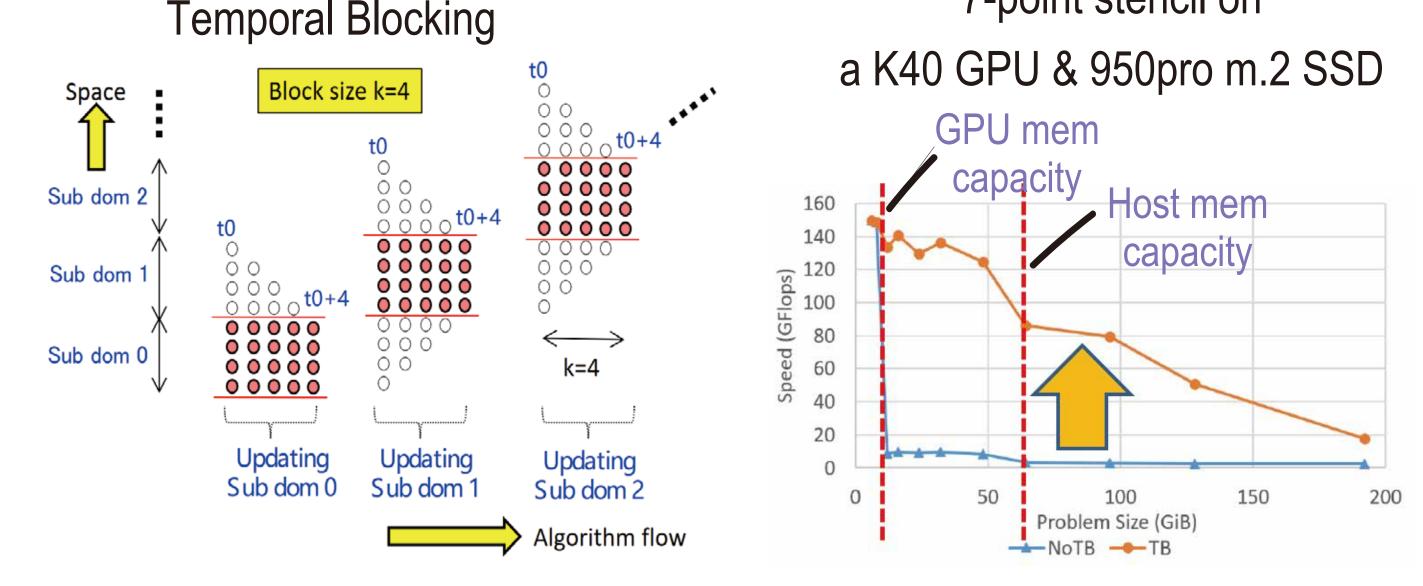

**Temporal blocking for stencil computation**

### **Motivation**

Towards achieving fast&big simulations, we need to exploit high speed of upper memory layer (e.g. GDDR/HBM on GPUs) and large capacity of lower memory layer (e.g. NAND Flash).

However, programming with consideration of memory hierarchy is troublesome.

### **Overview**

To make memory hierarchy programming easier, we implemented system software, named *HHRT (hybrid hierarchical runtime)*. • HHRT automatically supports data swapping between GPU memory and lower layer memory (host memory, Flash SSD) • HHRT supports "process-wise" swapping, not "page-wise" like OS. • HHRT is used by user programs written in MPI and CUDA. It is a wrapper library for MPI/CUDA.

• Programmers still have responsibility to improve locality for better performance

HHRT enables "larger" execution then upper memory, but app execution suffers from larger swapping cost, especially for stencil computation that has worse memory access locality.

A well known technique, "Temporal Blocking" (TB), which improves locality of stencil, achieves reasonable performance on HHRT. 7-point stencil on

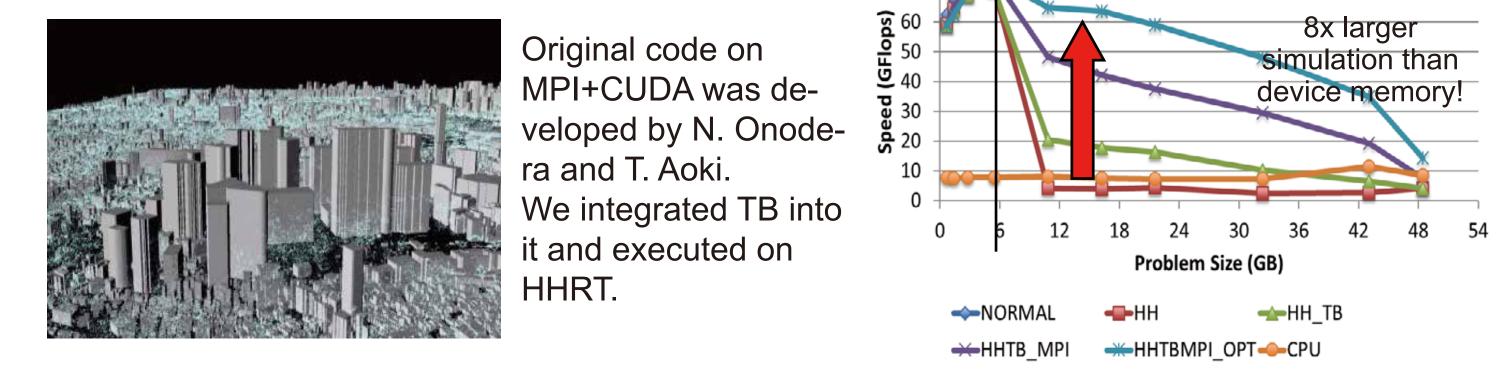

### **Integration with Real Simulation Application**

We integrated our techniques with stencil-based city airflow simulation.

Airflow performance on a K20X GPU

70

http://www.gsic.titech.ac.jp/sc16

### https://github.com/toshioendo/hhrt

T. Endo, G. Jin: Software Technologies Coping with Memory Hierarchy of GPGPU Clusters for Stencil Computations. IEEE Cluster 2014. T. Endo, Y. Takasaki, S. Matsuoka: Realizing Extremely Large-Scale Stencil Applications on GPU Supercomputers. IEEE ICPADS 2015. T. Endo: Realizing Out-of-Core Stencil Computations using Multi-Tier Memory Hierarchy on GPGPU Clusters. IEEE Cluster 2016.

PI: Toshio Endo (Tokyo Tech, endo@is.titech.ac.jp), supported by JST-CREST